ISSN 2066 - 8562

Volume **3**. Number **2/2010**

# LOW CURRENT REFERENCES WITH SUPPLY INSENSITIVE BIASING

Vlad ANGHEL<sup>1</sup>, Gheorghe BREZEANU<sup>2</sup>

**Abstract.** A comparison between three low current, self-biased current references, in two different configurations, is presented. Channel length modulation effects are taken into account in order to obtain the current dependence on the power-supply voltage variation. Analytical predictions are validated by comparison with simulated curves and measurement data. Moreover, sensitivity is considered, as a design parameter to describe power-supply voltage change effect on the reference output current.

Keywords: IC (integrated circuit), self-biasing, low current mirrors, Widlar configuration

#### 1. Introduction

Current references are among the most popular block because they are widely used in IC biasing [1]–[7]. Furthermore, as the microelectronic industry is becoming ever more competitive, power consumption is now a main concern. Currents in the range of microamps and less are required in a variety of the applications in order to minimize power dissipation. Such low currents can be generated with current mirrors, in which the transistors operate with unequal gate-source voltage. In addition, the use of self-biasing techniques dramatically increases the output current's independence to power-supply variations.

This paper is focused on three low current mirrors with self-biasing. The performance of these references is described by simulations, analytical models and measurements. The expressions of the sensitivity of the output current to power-supply voltage variations are obtained for the first time.

#### 2. Low current references

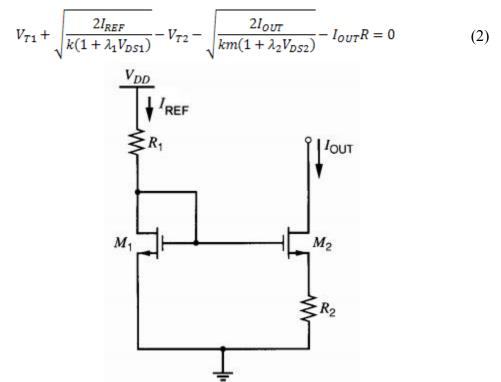

One of the most widespread low current mirrors uses a Widlar configuration. In this scheme a moderate resistor is inserted in series with the output transistor of a simple mirror as shown in Fig. 1 [6]. Moreover, the circuit is less sensitive to the input current and the supply voltage than the simple current mirror. A first view analysis of the Widlar current reference starts with the loop consisting of  $M_1$ ,  $M_2$  and  $R_2$ :

$$V_{GS1} - V_{GS2} - I_{OUT}R_2 = 0 \tag{1}$$

<sup>&</sup>lt;sup>1</sup>Ph.D., Eng. University "Politehnica" of Bucharest, Romania, vlad.anghel@onsemi.com.

<sup>&</sup>lt;sup>2</sup>Prof. univ. Ph.D., University "Politehnica" of Bucharest, Romania. Corresponding member of the Academy of Romanian Scientists; gheorghe.brezeanu@dce.pub.ro.

Due to the fact that the Widlar current source is capable of generating currents even in the range of nanoampers, transistors can operated in both strong and weak inversion. First, the transistors are biased in strong inversion. Given that  $I_{REF} > 0$ ,  $M_1$  operates in the active region because it is diode connected. Assuming that  $M_2$ also operates in the active region, expanding (1) gives:

Fig. 1. The simple Widlar current source.

where  $V_{TI}$  and  $V_{T2}$  are the threshold voltages of the transistors and k is the current factor of  $M_1$ . m - the multiplicity factor is defined as the ratio between the aspect factors (W/L) of  $M_2$  and  $M_1$ . The channel length modulation factors,  $\lambda_1$  and  $\lambda_2$ , are also taken into account. The drain-source voltage of  $M_1$  is equal to the difference between  $V_{DD}$  and the voltage drop on  $R_1$ . This dependence is responsible for the current's variation to power-supply.

Grouping in (2) the terms from the first member in the manner shown below:

$$(V_{T1} - V_{T2}) + \sqrt{\frac{2}{k}} \left( \sqrt{\frac{I_{REF}}{(1 + \lambda_1 V_{DS1})}} - \sqrt{\frac{I_{OUT}}{m(1 + \lambda_2 V_{DS2})}} \right) - I_{OUT}R = 0$$

(3)

results in two different ways in which the output current can be controlled. However  $I_{OUT}$  can be generated by the difference in either threshold voltages or in aspect ratios (m>1). Considering only the difference in aspect ratios, yields:

$$\sqrt{\frac{2}{k}} \left( \sqrt{\frac{I_{REF}}{(1 + \lambda_1 (V_{DD} - I_{REF} R_1))}} - \sqrt{\frac{I_{OUT}}{m(1 + \lambda_2 V_{DS2})}} \right) - I_{OUT} R = 0$$

(4)

If the transistors operate in weak inversion, (4) is replaced by:

$$\left(V_{T1} - V_{T2}\right) + n_s V_{th} \left[ \ln \left[ \frac{I_{REF}}{I'_s} \left( \frac{L}{W} \right)_1 \right] - \ln \left[ \frac{I_{OUT}}{I'_s} \left( \frac{L}{W} \right)_2 \right] \right] - I_{OUT} R = 0$$

(5)

If the threshold voltages are the same value, (5) becomes:

$$n_s V_{th} \ln \left[ \frac{I_{REF}}{I_{OUT}} m \right] - I_{OUT} R = 0 \tag{6}$$

The solution to  $I_{OUT}$  from (6) can be calculated by means of iterations. This analytical drawback is compensated by the power-supply independence – an advantage of weak inversion operation.

Manufacturing technologies also allow the use of MOS devices with various threshold voltages. Therefore, if  $M_1$  and  $M_2$  have different threshold voltages and the same aspect factor (m = 1), eq.(3) becomes:

$$(V_{T1} - V_{T2}) + \sqrt{\frac{2}{k}} \left( \sqrt{\frac{I_{REF}}{(1 + \lambda_1 (V_{DD} - I_{REF} R_1))}} - \sqrt{\frac{I_{OUT}}{(1 + \lambda_2 V_{DS2})}} \right) - I_{OUT} R = 0$$

(7)

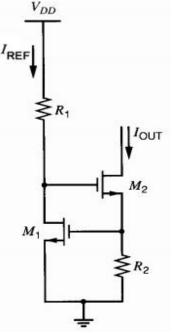

Fig. 2. Threshold referenced current source.

The level of power-supply independence given by the Widlar current reference is not adequate for many types of analog circuits which require a much more stable current source. Such source can be obtained by causing bias currents in the circuit to depend on a voltage standard other than the supply voltage [1]. The most convenient voltage standard is the threshold voltage of a MOS transistor. In Fig. 2 is presented a current reference based on this standard voltage. The advantage of creating a power-supply independent current source is counter-balanced by the fact that this type of source is quite temperature dependent.

The general formula for the current  $I_{OUT}$  is given from the loop containing the gate-source voltage of  $M_1$  and  $R_2$  (Fig. 2):

$$V_{GS1} - I_{OUT}R = 0 \tag{8}$$

As with the Widlar current source, the  $M_1$  channel length modulation factor ( $\lambda_1$ ), has been taken into account. The drain-source voltage of this transistor depends on V<sub>DD</sub>, thus (8) becomes:

$$V_{T1} + \sqrt{\frac{2I_{REF}}{k(1 + \lambda_1(V_{DD} - I_{REF}R_1))}} - I_{OUT}R = 0$$

(9)

#### 3. Self-biasing

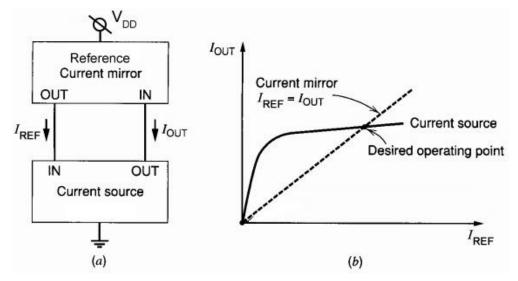

Self-biasing is a technique by which power-supply dependence can be greatly reduced. Instead of developing the input current by connecting a resistor to the supply, the input current is made to depend directly on the output current of the reference itself. The concept is illustrated in block-diagram form in Fig. 3a [1].

Fig. 3. (a) Block diagram of a self-biased reference. (b) Determination of operating point. [1]

The relationship between  $I_{REF}$  and  $I_{OUT}$  is governed by both the current source and the current mirror. From the standpoint of the current source, the output current is almost independent of the input current for a wide range of input currents as shown in Fig. 3b. From the standpoint of the current mirror,  $I_{REF}$  is set equal to  $I_{OUT}$ , assuming that the gain of the current mirror is unity. The operating point of the circuit must satisfy both constraints and hence is at the intersection of the two characteristics.

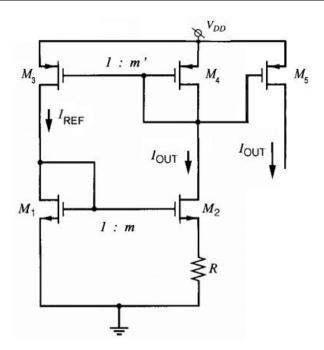

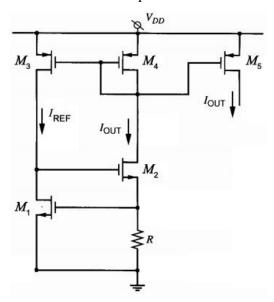

This enhancement can be applied to the simple Widlar current source. The resulting current reference is shown in Fig. 4. The current mirror comprises transistors  $M_3$ ,  $M_4$  and  $M_5$ , and establishes a connection between  $I_{REF}$  and  $I_{OUT}$  [3]. The input current  $I_{REF}$  is proportional to the output current  $I_{OUT}$  by a factor m'. Replacing  $I_{REF}$  in (3) yields:

$$(V_{T1} - V_{T2}) + \sqrt{\frac{2}{k}} \left( \sqrt{\frac{I_{OUT}}{m'(1 + \lambda_1 V_{DS1})}} - \sqrt{\frac{I_{OUT}}{m(1 + \lambda_2 V_{DS2})}} \right) - I_{OUT}R = 0$$

(10)

This equation is a cornerstone because it eliminates the input current, it allows the precise calculation of the output current and it also predicts its variation with the power-supply voltage ( $V_{DD}$ ).

The drain-source voltage of  $M_1$  is equal to its gate-source voltage, and the drainsource voltage of  $M_2$  is equal to the difference between the power-supply and the gate-source voltage of  $M_4$ . Also, considering that  $M_1$  and  $M_2$  have the same threshold voltages, (10) becomes:

$$\sqrt{I_{OUT}} \left[ \sqrt{\frac{2}{k}} \left( \sqrt{\frac{1}{m'(1 + \lambda_1 V_{GS1})}} - \sqrt{\frac{1}{m(1 + \lambda_2 (V_{DD} - V_{GS4}))}} \right) - \sqrt{I_{OUT}} R \right] = 0$$

(11)

Equation (11) has two solutions for  $I_{OUT}$ , one being zero (see Fig. 3b), and the other:

$$\sqrt{I_{OUT}} = \sqrt{\frac{2}{kR^2}} \left( \sqrt{\frac{1}{m'(1 + \lambda_1 V_{GS1})}} - \sqrt{\frac{1}{m(1 + \lambda_2 (V_{DD} - V_{GS4}))}} \right)$$

(12)

Expression (12) proves that  $I_{OUT}$  is dependent only of R, m and m' – parameters which can all be controlled during the design process. Furthermore, this equation also shows the variation of  $I_{OUT}$  in respect to  $V_{DD}$ . If the transistors operate in weak inversion, eq.(6) must be taken into consideration. This equation for self-biasing yields:

$$I_{OUT} = \frac{n_s V_{th}}{R} \ln\left[\frac{m}{m'}\right] \tag{13}$$

Fig. 4. The self biased Widlar current source

A simple solution to the output current is obtained which depends only of the resistance R and the multiplicity factors m and m'. Furthermore, the current does not vary with the supply voltage or the gate-source voltage of the transistors.

When the  $M_1$  and  $M_2$  threshold voltages are different and m = m' = l, from (10) and (11) is obtained:

$$(V_{T1} - V_{T2}) + \sqrt{\frac{2}{k}} \left( \sqrt{\frac{I_{OUT}}{(1 + \lambda_1 V_{GS1})}} - \sqrt{\frac{I_{OUT}}{(1 + \lambda_2 (V_{DD} - V_{GS4}))}} \right) - I_{OUT}R = 0$$

(14)

Relation (15) is a second degree polynomial equation with  $\sqrt{I_{OUT}} \sqrt{I_{OUT}}$  as the variable. The relevant solution to this equation is:

$$\sqrt{I_{OUT}} = \sqrt{\frac{1}{2kR^2}} \left[ \left( \sqrt{\frac{1}{1 + \lambda_1 V_{GS1}}} - \sqrt{\frac{1}{1 + \lambda_2 (V_{DD} - V_{GS4})}} \right) + \left( \left( \sqrt{\frac{1}{1 + \lambda_1 V_{GS1}}} - \sqrt{\frac{1}{1 + \lambda_2 (V_{DD} - V_{GS4})}} \right)^2 + 2kR(V_{T1} - V_{T2}) \right)^{\frac{1}{2}} \right]$$

(15)

Although it is not an engineer-friendly formula, (15) shows that  $I_{OUT}$  depends on the resistance and the difference between threshold voltages. The other terms predict the current's variation with the supply voltage ( $V_{DD}$ ). If this variation is not to be considered, then all the parentheses containing the  $\lambda$  factor can be ignored, and the formula is reduced to a much simpler form.

Fig. 5. The self-biased threshold referenced current source.

The self-biased threshold referenced current source is presented in Fig. 5. The  $M_3$  and  $M_4$  have the same parameters, forcing  $I_{REF}$  to be equal to  $I_{OUT}$  [4]. However, the channel length modulation effect is taken into account to underline the current's dependency to power-supply. The  $\lambda_3$  and  $\lambda_4$  factors have a value of 0.02 V<sup>-1</sup>. Considering these aspects in (9) yields:

$$V_{T1} + \sqrt{I_{OUT}} \sqrt{\frac{2(1 + \lambda_3(V_{DD} - V_{GS1} - V_{GS2}))}{k(1 + \lambda_1(V_{GS1} + V_{GS2}))(1 + \lambda_4 V_{GS4})}} - I_{OUT}R = 0$$

(16)

The solution of this equation is:

$$\sqrt{I_{OUT}} = \sqrt{\frac{(1 + \lambda_3 (V_{DD} - V_{GS1} - V_{GS2}))}{2kR^2 (1 + \lambda_1 (V_{GS1} + V_{GS2}) (1 + \lambda_4 V_{GS4})}} + \sqrt{\frac{(1 + \lambda_3 (V_{DD} - V_{GS1} - V_{GS2}))}{2kR^2 (1 + \lambda_1 (V_{GS1} + V_{GS2})) (1 + \lambda_4 V_{GS4})}} + \frac{V_{T1}}{R}}$$

(17)

In (17), the value of  $I_{OUT}$  is mainly determined by the  $V_{T1}$  / R ratio. The terms which include  $\lambda$  parameters are responsible for a slight output current variation with the power-supply voltage. Although of small magnitude, this variation

should be considered when precise results are required. Note that this threshold referenced current source needs a higher minimum supply voltage (with an additional threshold voltage) as opposed to the Widlar reference.

#### 4. Supply sensitivity

A measure of a circuit's stability with the power-supply variation is the sensitivity. Sensitivity describes how much a fractional change in power-supply triggers a fractional change in output current. The general formula for sensitivity is defined as follows [2]:

$$S_{V_{DD}}^{I_{OUT}} = \lim_{\Delta x \to 0} \frac{\Delta I_{OUT} / I_{OUT}}{\Delta V_{DD} / V_{DD}} = \frac{V_{DD}}{I_{OUT}} \frac{\partial I_{OUT}}{\partial V_{DD}}$$

(18)

The less the value of  $S_{V_{DD}}^{I_{OUT}}$ , the  $I_{OUT}$  is insensitive with  $V_{DD}$ . In the case of the simple current mirror, the sensitivity of the output current to power-supply variations is approximately unity, meaning that a 10% variation in  $V_{DD}$  translates into a equal variation in  $I_{OUT}$  [1]. For a simple Widlar current source (Fig. 1) the sensitivity is approximately 0.5 [1]; thus the same 10% variation of power-supply results only in a 5% change of output current. This improvement can be taken even further with the threshold referenced current source. The sensitivity, in this case is around 0.045 [1]. This source is not fully independent with power-supply because the gate-source voltage of  $M_1$  changes slightly with the supply voltage.

The use of self-biasing techniques significantly reduces power-supply sensitivity. In the case of the self-biased Widlar reference with different multiplicity factors, the sensitivity can be calculated by considering (12) and (18):

$$S_{V_{DD}}^{I_{OUT}} = \frac{\lambda_2 V_{DD}}{1 + \lambda_2 (V_{DD} - V_{GS4})} \left[ \frac{\sqrt{\frac{m'(1 + \lambda_1 V_{GS1})}{m(1 + \lambda_2 (V_{DD} - V_{GS4}))}}}{1 - \sqrt{\frac{m'(1 + \lambda_1 V_{GS1})}{m(1 + \lambda_2 (V_{DD} - V_{GS4}))}}} \right]$$

(19)

Using standard CMOS technology data, the power-supply sensitivity is between 0.05 and 0.1 in this case. If the self-biased Widlar current source uses transistors with different threshold voltages, then the formula for sensitivity is:

$$S_{V_{DD}}^{I_{OUT}} = \frac{\lambda_2 V_{DD}}{1 + \lambda_2 (V_{DD} - V_{GS4})} \frac{\left[1 + \frac{\left(\frac{1}{\sqrt{1 + \lambda_1 V_{GS1}}} - \frac{1}{\sqrt{1 + \lambda_2 (V_{DD} - V_{GS4})}}\right)}{\sqrt{2kR(V_{T1} - V_{T2})}}\right]^2}{\left[2kR(V_{T1} - V_{T2})(1 + \lambda_2 (V_{DD} - V_{GS4}))\right]^{\frac{1}{2}}}$$

(20)

In this situation, the power-supply sensitivity varies within a small range (0.04 - 0.05), if considering the standard CMOS models.

## 5. Results. Discussion

The self-biased current references previously presented have been simulated in a Hspice environment using professional MOS device models, from a standard 0.5  $\mu$ m CMOS process which represent the classical technology for analogue applications.

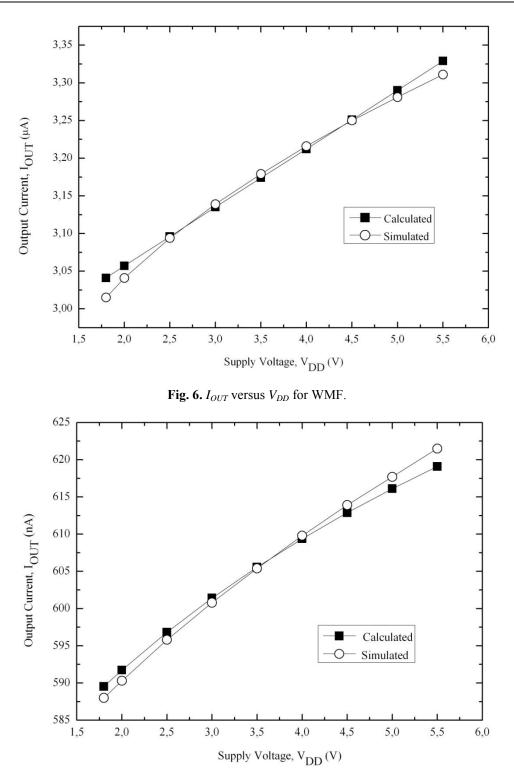

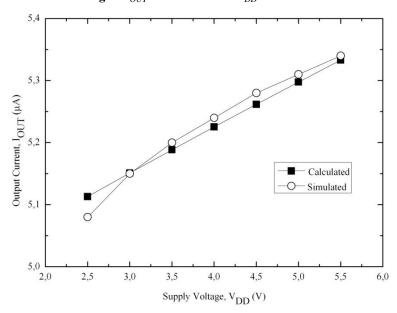

The purpose of these simulations is to prove analytical predictions. The powersupply varies in a typical low voltage range, between 1.8 and 5.5 V. Also, output currents for each reference source have been selected as to cover a wide range of applications.

In Table 1 are given all the relevant parameters used in simulations for each current source. The references have been abbreviated as follows: the self-biased Widlar current references with different multiplicity factors and different threshold voltages – WMF and respectively WTV, and the self-biased threshold referenced current source – TVR.

| Current | Parameter                  |               |   |    |                      |                      |                   |                                |  |

|---------|----------------------------|---------------|---|----|----------------------|----------------------|-------------------|--------------------------------|--|

| Source  | $k \left[\mu A/V^2\right]$ | <i>R</i> [kΩ] | m | m' | $\lambda_1 [V^{-1}]$ | $\lambda_2 [V^{-1}]$ | $V_{\rm T1}$ [mV] | $V_{\mathrm{T2}}[\mathrm{mV}]$ |  |

| WMF     | 216.25                     | 10.6          | 4 | 2  | 0.070                | 0.010                | 652               | 652                            |  |

| WTV     | 122.50                     | 661.0         | 1 | 1  | 0.090                | 0.200                | 652               | 290                            |  |

| TVR     | 116.00                     | 202.0         | 1 | 1  | 0.094                | 0.094                | 742               | 742                            |  |

Table 1. Parameters used in simulations and analytical model

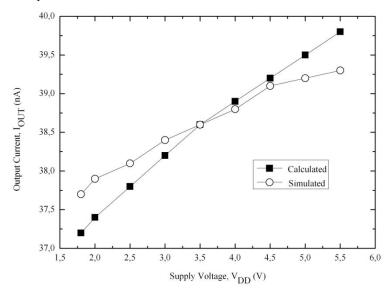

The output currents as a function of the supply voltage for all investigated current sources are given in Figs. 6 - 8. A comparison between simulations and analytical model, based on eqs. (12), (15) and (17), was performed. The curves for all three configurations show a very good agreement between the calculated and simulated data (within a 1% relative error).

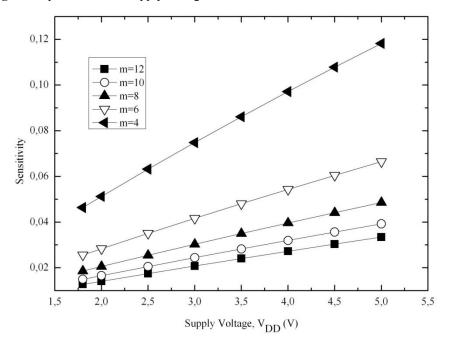

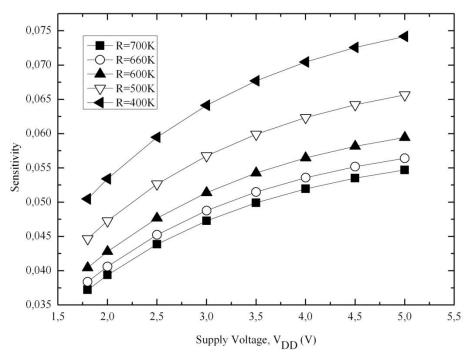

According to (19) and (20), the power-supply sensitivity for the Widlar mirrors changes with  $V_{DD}$ . In the case of WMF reference, the sensitivity can be controlled by the multiplicity factors of the mirrors in the design flow. Higher values of m results in a smaller sensitivity, as seen in Fig. 9. The rise slope of the sensitivity with  $V_{DD}$ , also decreases at high values of the multiplicity factor. Furthermore, the output current is dependent of both R and m (eq.(12)), whereas the sensitivity varies only with m. This conclusion has multiple benefits, such as changing the value of  $I_{OUT}$  without altering the sensitivity, or improving the sensitivity without altering  $I_{OUT}$ .

**Fig. 7.**  $I_{OUT}$  as a function of  $V_{DD}$  for WTV.

Fig. 8. Output current vs. supply voltage for the self-biased threshold referenced source.

Fig. 9. Output current to power-supply sensitivity for WMF, for different values of the multiplicity factor m (m'=2).

In the case of WTV reference, according to (20), sensitivity depends mainly on the resistor *R*, as shown in Fig. 10. Using a 660 k $\Omega$  resistor and the parameters from Table 5.1, the current source's sensitivity scales between 0.04 and 0.055.

Relative to the data from Fig. 9 and Fig. 10, we can observe that for any  $V_{DD}$ , the Widlar mirror using MOS transistors with different threshold voltages is less sensitive to power-supply variations. In addition, the sensitivity for WTV reference has a smaller variation with  $V_{DD}$  than WMF source. Nonetheless, the sensitivity for both types of self-biased current references is significantly smaller than that of a simple Widlar current source. Therefore the power-supply insensitivity is improved by five to ten times, by using self-biasing techniques.

Fig. 10. Output current to power-supply sensitivity for WTV.

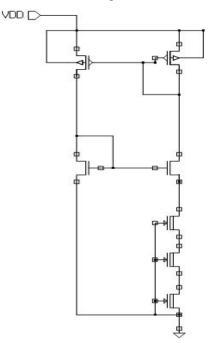

#### 6. Very low Widlar current source

To obtain very low currents (nA) using a Widlar configuration needs that the transistors to operate in weak inversion. In Fig. 11 a standard self-biased Widlar current source with MOS transistors biased in weak inversion is presented. This mirror is usually included in analog circuits such as comparators or oscillators for biasing purposes. The resistor R is implemented by depletion MOS transistors in order to minimize the area on the reference layout [7]. Table 2 contains values of the extracted parameters for the reference from Fig. 12.

| [ | $R$ [k $\Omega$ ] | т | m´ | n <sub>s</sub> | $V_{\rm th}[{ m mV}]$ | $I_{\rm s}'[\mu {\rm A}]$ | W/L | $V_{\rm T} [{ m mV}]$ |

|---|-------------------|---|----|----------------|-----------------------|---------------------------|-----|-----------------------|

| ĺ | 488               | 4 | 2  | 1.05           | 25                    | 3.39                      | 2.5 | 647                   |

Table 2. Parameters used in simulation and analytical model in weak inversion

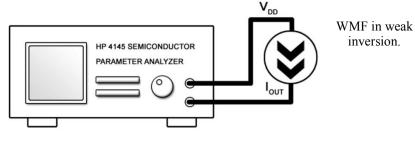

Measurements on the very low current source have been made using a HP 4145 Semiconductor Parameter Analyzer, with the basic setup from Fig. 11. The supply voltage was swept between 1.8 V and 5.5 V, with a step of 0.1 V. In order to minimize fabrication process variations, the output current has been considered as the average from twelve measured chips.

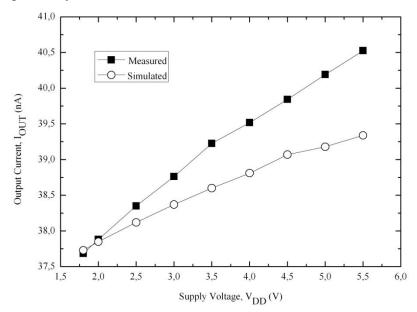

Fig. 13 shows a comparison between the simulated and experimental data of the output current of WMF reference with MOS operating in weak inversion. A good agreement of the simulated curve and the measured data has been achieved.

Fig. 11. Basic measurement setup for WMF in weak inversion.

Fig. 12. Basic measurement setup for WMF in weak inversion.

The output current increases with the supply voltage (Fig. 13). On the other hand, from (13), it can be observed that the output current is completely independent of power-supply variations. The  $I_D$  -  $V_{DD}$  dependence from Fig. 13 is caused by the slight change of  $M_2$  gate-source voltage, with  $V_{DD}$ . This variation was confirmed by the simulation results. In Table 3 is given the correspondence between  $V_{DD}$  and  $V_{GS2}$ , as reported by the simulations.

Fig. 13. Comparison of the simulation and measurements for WMF in weak inversion.

Fig. 14. Comparison between simulation and calculated data for WMF in weak inversion.

**Table 3.** The variation from simulations of the gate-source voltage of  $M_2$  vs the supply voltage for the reference from Fig. 11

| $V_{\rm DD}$ [V]       | 1.8 | 2   | 2.5 | 3   | 3.5 | 4   | 4.5 | 5   | 5.5 |

|------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| $V_{\rm GS2}[{ m mV}]$ | 504 | 504 | 505 | 505 | 505 | 506 | 506 | 506 | 506 |

Considering the variation in  $V_{GS2}$ , obtained in the simulation, and the transistor's operating in weak inversoin,  $I_{OUT}$ , has been calculated based on (13). The output current increases with the power-supply voltage as shown in Fig.14. The same good agreement with the simulated data is achieved.

### 7. Conclusions

Two configurations of the low current references, Widlar (with two schemes) and threshold referenced, have been studied in this paper. Analytical formulas for the references' output current, including the channel length modulation effect, are considered for both the simple and self-biased versions. The benefits of self biasing are underlined by the introduction of power-supply sensitivity. In order to validate the analytical results, simulations have been made in a Hspice environment, using standard CMOS  $0.5 \,\mu$ m models. Moreover, measurements have been made to further corroborate the previous results.

The sensitivity increases proportional to the power-supply voltage. This variation is greatly reduced by using the self-biasing technique. Although the sensitivity is diminished approximately ten times when self-biasing is applied. In the case of Widlar mirrors reference, the sensitivity can be controlled by the multiplicity factors of the mirrors in the design flow. The output current is dependent of both R and m whereas the sensitivity varies only with m. This behavior has multiple benefits, such as improving the sensitivity without shifting  $I_{OUT}$ . The self-biased Widlar reference with different threshold voltages is less sensitive to power-supply variations.

The output current's variation from all three current references can be predicted by means of analytical formulas, without the need for complex simulators. Also, the output current's sensitivity can be studied and adjusted. The analytical results of the output current and sensitivity are in good agreement with the simulated and the measured data.

# **REFERENCES**

[1] P. R. Gray, P. J. Hurst, S. H. Lewis, R. G. Meyer, "Analysis and Design of Analog IC's", Fourth Edition, J. Wiley & Sons, 2001.

[2] R. Jacob Baker, "CMOS. Circuit Design, Layout and Simulation", Revised Second Edition, Willey-IEEE, 2007.

[3] Behzad Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill, 2001.

[4] F. Maloberti, "Analog Design for CMOS VLSI Systems", Kluwer Academic Publishers, 2001.

[5] D. Johns, K. Martin, "Analog Integrated Circuit Design", J. Wiley & Sons, 1997.

[6] Gh. Brezeanu, F. Draghici, F. Mitu, Gh. Dilimot, "Fundamental Electronic Circuits", ALL Beck, 2005.

[7] V. Anghel, "Low Current Reference for Integrated Circuits Used in Portable Devices", Bachelor Degree Paper, 2009.